#### Members of the dissertation committee:

Prof. dr. ir. G.J.M. Smit University of Twente (promotor)

Dr. ir. J. Kuper University of Twente (assistant-promotor)

Prof. dr. J.C. van de Pol University of Twente Prof. dr. ir. B.R.H.M. Haverkort University of Twente

Prof. dr. M. Sheeran Chalmers University of Technology

Prof. dr. ir. T. Schrijvers Katholieke Universiteit Leuven

Prof. dr. K. Hammond University of St. Andrews

Prof. dr. K. Hammond University of St. Andrews

Prof. dr. P.M.G. Apers University of Twente (chairman and secretary)

## UNIVERSITY OF TWENTE.

Faculty of Electrical Engineering, Mathematics and Computer Science, Computer Architecture for Embedded Systems (CAES) group

This research is conducted within the Service-oriented Operating Systems (S(o)OS) project (Grant Agreement No. 248465) supported under the FP7-ICT-2009.8.1 program of the European Commission.

This research is conducted within the Programming Large Scale Heterogeneous Infrastructure (Polca) project (Grant Agreement No. 610686) supported under the FP7-ICT-2013.3.4 program of the European Commission.

CTIT Ph.D. thesis Series No. 14-335 Centre for Telematics and Information Technology University of Twente, P.O. Box 217, NL-7500 AE Enschede

Copyright © 2014 by Christiaan P.R. Baaij, Enschede, The Netherlands. This work is licensed under the Creative Commons Attribution 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

This thesis was typeset using  $\LaTeX$  2 $_{\epsilon}$ , TikZ, and Sublime Text. This thesis was printed by Gildeprint Drukkerijen, The Netherlands.

ISBN 978-90-365-3803-9

ISSN 1381-3617 (CTIT Ph.D. thesis Series No. 14-335)

DOI 10.3990/1.9789036538039

## DIGITAL CIRCUITS IN CλASH

### FUNCTIONAL SPECIFICATIONS AND TYPE-DIRECTED SYNTHESIS

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. H. Brinksma, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 23 januari 2015 om 14:45 uur

door

Christiaan Pieter Rudolf Baaij

geboren op 1 februari 1985 te Leiderdorp

## Dit proefschrift is goedgekeurd door:

Prof. dr. ir. G.J.M. Smit (promotor)

Dr. ir. J. Kuper (assistent promotor)

## **ABSTRACT**

Over the last three decades, the number of transistors used in microchips has increased by three orders of magnitude, from millions to billions. The productivity of the designers, however, lags behind. Designing a chip that uses ever more transistors is complex, but doable, and is achieved by massive replication of functionality. Managing to implement complex algorithms, while keeping non-functional properties, such as area and gate propagation latency, within desired bounds, and thoroughly verifying the design against its specification, are the main difficulties in circuit design.

It is difficult to measure design productivity *quantitatively*; transistors per hour would not be a good measure, as high transistor counts can be achieved by replication. As a motivation for our work we make a *qualitative* analysis of the tools available to circuit designers. Furthermore, we show how these tools manage the complexity, and hence improve productivity. Here we see that progress has been slow, and that the same techniques have been used for over 20 years. Industry standard languages, such as VHDL and (System)Verilog, do provide means for abstractions, but they are distributed over separate language constructs and have ad hoc limitations. What is desired is a single abstraction mechanism that can capture most, if not all, common design patterns. Once we can abstract our common patterns, we can reason about them with rigour. Rigorous analysis enables us to develop correct-by-construction transformations that capture trade-offs in the non-functional properties. These correct-by-construction transformations give us a straightforward path to reaching the desired bounds on non-functional properties, while significantly reducing the verification burden.

We claim that functional languages can be used to raise the abstraction level in circuit design. Especially higher-order functional languages, where functions are first-class and can be manipulated by other functions, offer a single abstraction mechanism that can capture many design patterns. An additional property of functional languages that make them a good candidate for circuit design is purity, which means that functions have no side-effects. When functions are pure, we can reason about their composition and decomposition locally, thus enabling us to reason formally about transformations on these functions. Without side-effects, synthesis can derive highly parallel circuits from a functional description because it only has to respect the direct data dependencies.

In existing work, the functional language *Haskell* has been used as a host for *embedded* hardware description languages. An embedded language is actually a set of

data types and expressions described within the host language. These data types and expressions then act like the keywords of the embedded language. Functions in the host language are subsequently used to model functions in the embedded language. Although many features of the host language can be used to model equivalent behaviour in the embedded language, this is not true for all features. One of the most important features of the host language that cannot directly be used in the embedded language, are features that model choice, such as pattern matching.

This thesis explores the idea of using the functional language Haskell *directly* as a hardware specification language, and move beyond the limitations of embedded languages. Additionally, where applicable, we can use normal functions from existing Haskell libraries to model the behaviour of our circuits.

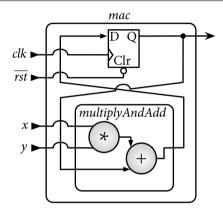

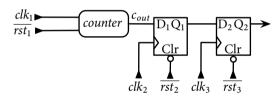

There are multiple ways to interpret a function as a circuit description. This thesis makes the choice of interpreting a function definition as a *structural* composition of components. This means that every function application is interpreted as the component instantiation of the respective sub-circuit. Combinational circuits are then described as functions manipulating algebraic data types. Synchronous sequential circuits are described as functions manipulating infinite streams of values. In order to reduce the cognitive burden, and to guarantee synthesisable results, streams cannot be manipulated directly by the designer. Instead, our system offers a limited set of combinators that can safely manipulate streams, including combinators that map combinational functions over streams. Additionally, the system offers streams that are explicitly synchronised to a particular clock and thus enable the design of multi-clock circuits. Proper synchronisation between clock domains is checked by the type system.

This thesis describes the inner workings of our  $C\lambda aSH$  compiler, which translates the aforementioned circuit descriptions written in Haskell to low-level descriptions in VHDL. Because the compiler uses Haskell directly as a specification language, synthesis of the description is based on (classic) static analysis. The challenge then becomes the reduction of the higher-level abstractions in the descriptions to a form where synthesis is feasible. This thesis describes a term rewrite system (with bound variables) to achieve this reduction. We prove that this term rewrite system *always* reduces a polymorphic, higher-order circuit description to a synthesisable variant. The only restriction is that the root of the function hierarchy is not polymorphic nor higher-order. There are, however, no restrictions on the use of polymorphism and higher-order functionality in the rest of the function hierarchy.

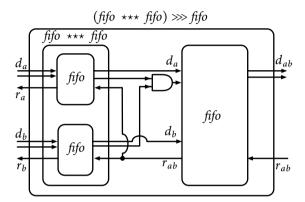

Even when descriptions use high-level abstractions, the  $C\lambda aSH$  compiler can synthesize efficient circuits. Case studies show that circuits designed in Haskell, and synthesized with the  $C\lambda aSH$  compiler, are on par with hand-written VHDL, in both area and gate propagation delay. Even in the presence of contemporary Haskell idioms and abstractions to write imperative code (for a control-oriented circuit), does the  $C\lambda aSH$  compiler create results with decent non-functional properties. To emphasize that our approach enables correct-by-construction descriptions, we demonstrate abstractions that allow us to automatically compose components that

vii

use back-pressure as their synchronisation method. Additionally, we show how cycle delays can be encoded in the type-signatures of components, allowing us to catch any synchronisation error at compile-time.

This thesis thus shows the merits of using a modern functional language for circuit design. The advanced type system and higher-order functions allow us to design circuits that have the desired property of being correct-by-construction. Finally, our synthesis approach enables us to derive efficient circuits from descriptions that use high-level abstractions.

## SAMENVATTING

Gedurende de laatste drie decennia is het aantal transistors in een processor met drie ordegroottes toegenomen, van miljoenen naar miljarden. De productiviteit van de ontwerpers loopt hier echter op achter. Het ontwerpen van een processor met telkens meer transistors is complex, maar doenlijk, en wordt bereikt door het veelvuldig kopiëren van functionaliteit. Het implementeren van complexe algoritmes, en het daarbij in toom houden van niet-functionele aspecten, zoals oppervlakte en propagatievertraging, en het zorgvuldig verifiëren van het uiteindelijke ontwerp, zijn de voornaamste moeilijkheden in het ontwerpen van digitale circuits.

Het is moeilijk om productiviteit van ontwerpers kwantitatief te bepalen; transistors per uur is geen goede maat, omdat hoge transistoraantallen kunnen worden bereikt door replicatie van functionaliteit. Als motivatie voor ons werk maken we een kwalitatieve analyse van de software die beschikbaar is voor ontwerpers van digitale circuits. Hierbij laten we zien hoe deze software helpt bij het beheersen van de complexiteit en dus de productiviteit verhoogt. We zien dan een geringe voortgang, waarbij dezelfde technieken al meer dan 20 jaar worden gebruikt. Talen die de standaard zijn in de industrie, zoals VHDL en (System)Verilog, verschaffen wel abstractiemogelijkheden, maar deze zijn verspreid over verschillende delen van de taal en hebben ad hoc beperkingen. Het is wenselijk om één abstractiemechanisme te hebben waarmee we veel, dan niet alle, ontwerppatronen kunnen uitdrukken. Wanneer we onze ontwerppatronen kunnen abstraheren, kunnen we er ook grondig over redeneren. Grondige analyses staan ons toe om inherent correcte transformaties te ontwerpen die afwegingen van niet-functionele eigenschappen uitdrukken. Omdat deze transformaties inherent correct zijn, is het mogelijk om tot een ontwerp te komen met de gewenste niet-functionele eigenschappen, zonder dat we extra verificatiestappen hoeven te ondernemen.

Wij beweren dat functionele talen zeer geschikt zijn om het abstractieniveau, van het ontwerpen van digitale circuits, naar een hoger niveau te tillen. Zeker hogereorde functies, waar functies andere functies kunnen bewerken, zijn geschikt als

enkel abstractiemechanisme voor vele ontwerppatronen. Een andere eigenschap

van functionele talen die ze geschikt maakt voor het ontwerpen van digitale circuits

is dat functies vrij zijn van neveneffecten. Omdat functies geen neveneffecten hebben kunnen we op lokaal niveau redeneren over de compositie en decompositie van

functies, en zodanig ook formeel redeneren over transformaties van deze functies.

Vrij van neveneffecten, kan het syntheseproces zeer parallelle circuits afleiden van

zo'n functionele beschrijving, omdat er alleen rekening gehouden hoeft te worden

met directe afhankelijkheden.

In bestaand werk is er gekeken naar het gebruik van de functionele taal *Haskell* als kadertaal voor *ingebedde* hardwarebeschrijvingstalen. Zo'n ingebedde taal is eigenlijk een verzameling van datatypes en functies beschreven in de kadertaal, waar deze functies en datatypes dienen als trefwoorden van de ingebedde taal. Alhoewel vele aspecten van de kadertaal gebruikt kunnen worden om equivalente aspecten in de ingebedde taal uit te drukken, geldt dat niet zo voor alle aspecten van de kadertaal. Eén van de belangrijkste aspecten van de kadertaal die niet in de ingebedde taal gebruikt kan worden, zijn de aspecten die keuze uit kunnen drukken, zoals patroonherkenning.

Dit proefschrift verkent het idee om de functionele taal Haskell *direct* als hardwaresbeschrijvingstaal te gebruiken, zodat we niet meer onderhevig hoeven te zijn aan de beperkingen van ingebedde talen. Daarbij is het dan ook mogelijk, waar dat van toepassing is, om direct functies uit de standaardbibliotheken te gebruiken voor het beschrijven van digitale circuits.

Er zijn meerdere manieren om een functie als digitaal circuit te interpreteren. In dit proefschrift kiezen wij ervoor om functies te interpreteren als een *structurele* compositie van componenten. Dit betekent dat elke toegepaste functie wordt geïnterpreteerd als een nieuwe instantie van het overeenkomstige circuit. Combinatorische circuits worden beschreven als functies die algebraïsche datatypes bewerken. Synchroon sequentiële circuits worden beschreven als functies die oneindig lange reeksen van waarden bewerken. Om de cognitieve last te verlichten, en om synthetiseerbare resultaten te garanderen, kunnen zulke oneindige reeksen van waarden niet direct bewerkt kunnen worden de ontwerper. In plaats daarvan biedt het systeem een beperkte set van functies die de ontwerper toe staan de reeks op een bepaalde manier te bewerken, zoals een functie die elementsgewijs een combinatorische functie toepast op de reeks van waarden. Daarbij zijn er reeksen die expliciet zijn gekoppeld aan een specifieke klok, welk het mogelijk maakt om circuits te ontwerpen met meerdere klokken. Correcte overgangen tussen de klokdomeinen worden gecontroleerd door het typesysteem.

Dit proefschrift beschrijft de interne werking van de  $C\lambda$ aSH *compiler*, welk eerdergenoemde circuitbeschrijvingen in Haskell omzet naar laag-niveau beschrijvingen in VHDL. Omdat de compiler Haskell direct als specificatietaal gebruikt, is synthese gebaseerd op (klassieke) statische analyse. De uitdaging zit dan in het reduceren van de hoog-niveau abstractiemechanismen die zich bevinden in de beschrijvingen naar een vorm waar synthese doenlijk is. Dit proefschrift beschrijft een termherschrijfsysteem (met gebonden variabelen) om deze reductie te bereiken. We bewijzen dat dit termherschrijfsysteem *altijd* polymorfe hogere-orde beschrijvingen van circuits reduceert naar een synthetiseerbare variant. De enige beperking is dat de functie bovenaan in de functiehiërarchie niet polymorf noch van hogere-orde is. Er zijn echter geen beperkingen in de rest van die functiehiërarchie wat betreft het gebruik van polymorfisme en hogere-orde functionaliteit.

Zelfs wanneer de beschrijvingen abstracties van een hoog niveau bevatten is de  $C\lambda$ aSH compiler in staat hiervan efficiënte circuits te synthetiseren. Casestudies

laten zien dat circuits die zijn ontworpen in Haskell, en gesynthetiseerd zijn met  $C\lambda aSH$ , gelijkwaardig zijn aan circuits direct ontworpen in VHDL, zowel in grootte als in propagatievertraging. Ook wanneer eigentijdse Haskell idiomen worden gebruikt om imperatieve code (voor een controlegeoriënteerd circuit) te schrijven is de  $C\lambda aSH$  compiler in staat om resultaten te genereren met degelijke nietfunctionele aspecten. Om te benadrukken dat onze aanpak de gelegenheid geeft om inherent correcte beschrijvingen te ontwerpen, demonstreren wij abstracties die het mogelijk maken om circuits met elkaar te verbinden die tegendruk gebruiken als synchronisatiemethode. Ook laten we zien hoe klokslagvertragingen aan de typesignaturen van componenten kunnen worden toegevoegd, zodat we incorrecte synchronisatie tussen componenten al kunnen afvangen op het moment van ontwerpen.

Dit proefschrift laat dus zien waarom een moderne functionele taal zeer geschikt is voor het ontwerpen van digitale circuits. Het geavanceerde typesysteem en de hogere-orde functies maken het mogelijk om ontwerpen te maken die inherent correct zijn. Tenslotte zorgt onze syntheseaanpak ervoor dat we efficiënte circuits kunnen afleiden van beschrijvingen welke abstracties van een hoog niveau bevatten.

## Dankwoord

November 2008, ik was op zoek naar een masteropdracht, januari 2015, ik ga promoveren. Zes jaar lang gewerkt aan hetzelfde onderwerp, waarvan het laatste jaar voornamelijk aan dit boekje. Ondertussen werken er al meerdere mensen, zelfs van buiten de vakgroep, met de software die er is geschreven, iets waar ik zeer tevreden over ben. Ook al geloof je in je eigen verhaal, geeft het toch een grote voldoening wanneer ook andere mensen jouw werk nuttig en interessant vinden.

Gedurende deze reis van zes jaar zijn er vele mensen die mij hebben geholpen met mijn werk, en nog belangrijker, ze hebben er voor gezorgd dat ik het altijd naar mijn zin heb gehad. Daarvoor wil ik hun graag bedanken.

Jan, voor de introductie tot de beste manier van programmeren, maar ook onze plezierige en uitgebreide discussies tijdens de reizen door heel Europa. Bij de eerste projectvergaderingen van SoOS had ik echt het gevoel alsof we daar niks hadden gedaan, maar daar wist jij dan altijd wel weer een positieve draai aan te geven. Nu weet ik inmiddels dat niet alles in twee dagen geregeld kan worden. Gerard, voor het zorgen voor een plek waar ik de kans kreeg om onderzoek te doen wat ik leuk vind, en, wat toch zeker heeft bijgedragen dat ik wilde gaan promoveren, dat je een groep hebt gecreëerd waar ik me als masterstudent volwaardig lid van de groep voelde.

Koen, een goed klankboord voor al jouw continue wiskunde problemen was ik nooit, maar het is wel altijd gezellig met jou op de kamer. Of je nu zelfs een gevatte opmerking maakt, of onbedoeld een opmerking maakt waar iemand anders een gevat weerwoord op heeft, zorg je altijd voor veel humor op de groep. Arjan en Philip, voor het helpen bij het oplossen van problemen van een zekere functionele aard. Gerald, voor de eerste verkenning van tijdsannotaties op de functionele beschrijvingen. Rinse, Peter, Ruud, Jaco, Erwin, hoewel de compiler natuurlijk altijd wel werkte op *mijn* computer met *mijn* voorbeelden, ben ik toch blij met de vele testcode en bugreports die door jullie zijn geleverd. Jochem, voor de interessante discussies over bitcoin en andere politieke en financiële wereldzaken. Marlous, Thelma, en Nicole, voor het regelen van hotels, vliegreizen, en nog zo vele andere zaken. Marloes voor een gezellige afsluiting van de dag wanneer we samen naar huis fietsen. Karel en Tom, voor de mooie gesprekken tijdens pauzes, borrels, en onder het gamen, en natuurlijk onze gedeelde waardering voor films met een hoog TSH¹ gehalte.

<sup>&</sup>lt;sup>1</sup>Deze zal je niet terugvinden in de acronymenlijst.

xiv

Tenslotte, mijn geliefde Alexandra, voor het geduldig aanhoren als ik je terloops vertel dat ik de volgende dag voor een week weg ben voor conferentie, voor het vriendelijk herinneren dat de buren ook mijn geram op de toetsenbordplank kunnen horen, en het me bijstaan in vele achtereenvolgende weekenden toen ik doorwerkte aan dit boekje.

Christiaan Enschede, december 2014

## **CONTENTS**

| Int                                    | RODUCTION                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                    | Hardware Description Languages                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2                                    | Functional Hardware Description Languages  1.2.1 Sequential logic  1.2.2 Higher level abstractions  1.2.3 Challenges in synthesising functional HDLs to circuits | 6<br>7<br>9<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3                                    |                                                                                                                                                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.4                                    |                                                                                                                                                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.5                                    | Structure of the thesis                                                                                                                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ha                                     | rdware Description Languages                                                                                                                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1                                    | Introduction                                                                                                                                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2                                    | Standard hardware description languages  2.2.1 VHDL  2.2.2 Verilog  2.2.3 SystemVerilog  2.2.4 BlueSpec SystemVerilog  Functional Languages                      | 16<br>16<br>18<br>19<br>20<br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        | 2.3.1 Conventional Languages                                                                                                                                     | 21<br>26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4                                    | Conclusions 2.4.1 Standard Languages 2.4.2 Functional Languages                                                                                                  | 32<br>32<br>33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CAES Language for Synchronous Hardware |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1                                    | Introduction                                                                                                                                                     | 37<br>38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2                                    | Combinational logic  3.2.1 Function abstraction and application  3.2.2 Types  Choice                                                                             | 39<br>39<br>40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                        | 1.1 1.2 1.3 1.4 1.5 HAI 2.1 2.2  CAI 3.1                                                                                                                         | 1.2 Functional Hardware Description Languages 1.2.1 Sequential logic 1.2.2 Higher level abstractions 1.2.3 Challenges in synthesising functional HDLs to circuits  1.3 Research questions 1.4 Approach and contributions of the thesis 1.5 Structure of the thesis  HARDWARE DESCRIPTION LANGUAGES 2.1 Introduction 2.2 Standard hardware description languages 2.2.1 VHDL 2.2.2 Verilog 2.2.3 SystemVerilog 2.2.4 BlueSpec SystemVerilog 2.2.4 BlueSpec SystemVerilog 2.3.1 Conventional Languages 2.3.2 Embedded Languages 2.3.2 Embedded Languages 2.4.1 Standard Languages 2.4.1 Standard Languages 2.4.2 Functional Languages 2.4.1 Standard Languages 2.4.2 Functional Languages 3.1 Introduction 3.1.1 A structural view 3.2 Combinational logic 3.2.1 Function abstraction and application |

|   | 3.3             | Higher level abstractions 3.3.1 Polymorphism 3.3.2 Higher-order functions                                                                                | 45<br>45<br>48             |

|---|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 3.4             | Sequential logic  3.4.1 Synchronous sequential circuits  3.4.2 A safe interface for Signal  3.4.3 Abstractions over Signal  3.4.4 Multiple clock domains | 52<br>53<br>56<br>58<br>61 |

|   | 3.5             | Conclusions and future work                                                                                                                              | 66<br>68                   |

| 4 | Түр             | e-Directed Synthesis                                                                                                                                     | 71                         |

|   | 4.1             | Introduction                                                                                                                                             | 71                         |

|   |                 | 4.1.1 Netlists & Synthesis                                                                                                                               | 72                         |

|   | 4.2             | Compiler pipeline                                                                                                                                        | 74                         |

|   |                 | 4.2.1 System FC                                                                                                                                          | 75                         |

|   |                 | 4.2.2 Normal form                                                                                                                                        | 87                         |

|   |                 | 4.2.3 From normalised System FC to a netlist                                                                                                             | 88                         |

|   | 4.3             | Normalisation                                                                                                                                            | 95                         |

|   |                 | 4.3.1 Eliminating non-representable values                                                                                                               | 97                         |

|   |                 | 4.3.2 Completeness of non-representable value removal                                                                                                    | 105                        |

|   |                 | 4.3.3 Termination of non-representable value removal                                                                                                     | 115                        |

|   |                 | 4.3.4 Simplification                                                                                                                                     | 120                        |

|   | 4.4             | Discussion                                                                                                                                               | 125                        |

|   |                 | 4.4.1 Properties of the normalisation phase                                                                                                              | 125                        |

|   |                 | 4.4.2 Correspondence operational semantics and netlists                                                                                                  | 126                        |

|   |                 | 4.4.3 Recursive descriptions                                                                                                                             | 127                        |

|   | 4.5             | Conclusions                                                                                                                                              | 128                        |

|   |                 | 4.5.1 Future work                                                                                                                                        | 128                        |

| 5 | Adv             | vanced aspects of circuit design in CλaSH                                                                                                                | 135                        |

|   | 5.1             | Introduction                                                                                                                                             | 135                        |

|   | 5.2             | Streaming reduction circuit                                                                                                                              | 136                        |

|   | 5.3             | CλaSH demonstrator circuit                                                                                                                               | 141                        |

|   | 5.4             | Correct-by-construction compositions                                                                                                                     | 148                        |

|   | J• <del>•</del> | 5.4.1 Back pressure                                                                                                                                      | 148                        |

|   |                 | 5.4.2 Delay annotations                                                                                                                                  | 154                        |

|   | 5.5             | Discussion                                                                                                                                               | 158                        |

|   | 1.7             | P1000001011                                                                                                                                              |                            |

| 6                    | Conclusions               |                                 | 163 | xvi      |

|----------------------|---------------------------|---------------------------------|-----|----------|

|                      | 6.1                       | Contributions                   | 165 | AVI      |

|                      | 6.2                       | Recommendations                 | 165 |          |

| A                    | Firs                      | t Class Patterns in Kansas Lava | 169 | Contents |

| В                    | Synchronisation Primitive |                                 |     | Con      |

| С                    | Syst                      | тем FC                          | 177 |          |

| D                    | Pres                      | SERVATION OF THE REWRITE RULES  | 191 |          |

| ACRONYMS             |                           |                                 | 197 |          |

| Bibliography         |                           | 199                             |     |          |

| LIST OF PUBLICATIONS |                           | 207                             |     |          |

## 1

## Introduction

In 1985<sup>1</sup>, Intel released the 80386, a consumer-grade central processing unit (*CPU*) that had around 275.000 transistors. The Intel 80486, released 4 years later, was the first x86 CPU that crossed the 1 million transistor boundary. The largest available chip today, in terms of transistor count, is NVIDIA's GK110 GPU rounding out at about 7 billion transistors. Nearly three decades of technology scaling have thus increased the transistor count by three orders of magnitude: from millions to billions.

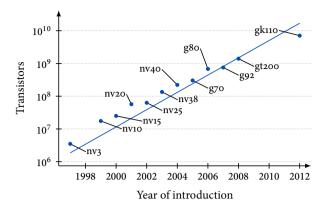

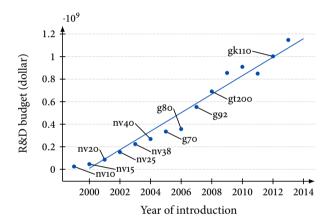

While transistor budgets grew by three orders of magnitude over three decades, it is much harder to determine whether the productivity of chip designer grew equally fast over the years. Figure 1.1 sets out the R&D budget of NVIDIA against the transistor count of their GPUs. We choose NVIDIA as their R&D is spent on a small product line, where the main product line is most likely taking up the largest part of their budget. If we would consider transistors per dollar spent as a measure for productivity, then NVIDIA's productivity is spectacular: while its R&D budget grows linearly, the number of transistors used in their GPU grows (almost) exponentially.

Such spectacular productivity growth is of course unlikely; it would have been wide-spread knowledge within the community if it would be true. Using the number of transistors as a measure for productivity is not a particularly good measure, these high transistor counts are achieved because GPUs are highly regular. GPUs fill their transistor budgets through replication: they consist out of hundreds, if not thousands, of identical cores. The same story holds for modern CPUs, for both mobile and desktop systems: they have multiple cores, sometimes in the double digits, and megabytes of cache memory. As replication is straightforward, the real complexity of these designs lies with their individual computational units and the composition of these units. When we would measure productivity in terms of transistors used for these individual units, the results are indeed not as spectacular.

<sup>&</sup>lt;sup>1</sup>Chosen as a reference as it corresponds to the author's date of birth.

Figure 1.1 – NVIDIA: GPU transistors vs. R&D budget<sup>2</sup>

We can derive from the above that, measuring productivity *quantitatively* is not straightforward; actually, we are not aware of any measure in circuit design that can give a good indication for productivity. We can still, however, try to *qualitatively* determine how the tools and methodologies have improved productivity over the years, and find out where there is room for even further improvement. We will focus on the tools that help shape the design, and serve as the main implementation tools for digital circuits: hardware description languages (*HDLs*).

<sup>&</sup>lt;sup>2</sup>Transistor counts are copied from http://en.wikipedia.org/wiki/Transistor\_count# GPUs. R&D budget are as reported on the annual 10-K reports (http://investor.nvidia.com/sec.cfm)

#### 1.1 HARDWARE DESCRIPTION LANGUAGES

The two most commonly used HDLs, VHDL and Verilog, were introduced when industry shifted circuit design towards very-large-scale integration (*VLSI*). At that time, these HDLs were used for the documentation and simulation of circuits that were *already* designed in a different format, for example with schematic capture tools. It is the advent of logic synthesis (and automated place & route) that really pushed VHDL and Verilog to the forefront of digital circuit design. Logic synthesis resulted in an incredible productivity boost compared to schematic capture tools and the manual layout process that were common practise until that time.

These logic synthesis tools work on register-transfer level (*RTL*) descriptions of a circuit. RTL describes a circuit in terms of the composition of the signals between registers, and the logical operations performed on those signals. In order to raise the abstraction level even further, and hence improve the productivity of circuit designer, the next step was to *just* describe the behaviour of the circuit, and *derive* an efficient structural description [43]. The two well-known approaches to facilitating better behavioural descriptions are:

- » Extending and improving existing HDLs with features from modern programming languages, such as the object-oriented features of SystemVerilog (an extension, now successor, to Verilog).

- » High-level synthesis (HLS) [13, 43] (or behavioural synthesis) of high level (programming) languages such as C or Java.

The purpose of high-level synthesis (*HLS*) is to transform a behavioural, often sequential, description of a circuit to an RTL description. HLS is not restricted to regular programming languages, it applies equally to the behavioural feature set of existing (and extended) HDLs. The code in listing 1.2 gives an RTL description of a finite impulse response (*FIR*) filter in VHDL. It is a fully parallel implementation. There is also one (purposefully included) performance issue: all multiplied values are added in a long chain, instead of using a tree of adders, leading to a longer combinational path than necessary.

The code in listing 1.1 gives a *behavioural* description of a FIR filter in C. The purpose of a HLS tool is to convert this behavioural description to an RTL description. It does not need to be a fully parallel implementation like the code in listing 1.2 though, it is also possible to map the description to a sequential implementation, one which contains only a single multiplier and a single adder. The process for determining whether the implementation should be fully parallel, fully sequential, or something in between, can either be done:

- » Manually: the HLS tool provides mechanisms to, e.g., unroll and pipeline loops.

- » Automatically: the HLS searches for an implementation that best fits the given size and latency restrictions.

```

void fir_filter

(int 16 * inp, int 16 coeffs [NUM_TAPS], int 16 * outp) {

static int16 regs [NUM_TAPS];

temp = 0;

int32

int

i;

for (i = NUM\_TAPS-1; i>=0; i--) {

if (i == 0)

regs[i] = *inp;

8

else

q

regs[i] = regs[i-1];

10

11

12

for (i = NUM\_TAPS-1; i>=0; i--) \{

13

temp += coeffs [i] * regs [i];

14

15

16

*outp = temp >> 16;

17

18

```

LISTING 1.1 - FIR Filter: Behavioural C description

For example, HLS tools can take the associativity of addition into account when summing the multiplied values and subsequently generate a tree of adder circuits automatically.

The uptake of higher-level languages for circuit design and verification in industry, be it a regular programming language or an extended HDL, is high. Use of SystemVerilog for verification and testing is considered common practise, especially in the ASIC design industry. Due to limited support from the synthesis tools, the higher level features of these HDLs are not used for the actual implementation description of a circuit. Uptake of HLS tools, such as C-to-Gates tools, is, however, much lower.

Early HLS tools, those introduced during the 1990's, showed a low adaptation for multiple reasons [41]: The quality of the generated hardware was much worse than hand-crafted designs, giving no incentive for RTL designers to switch. Also, these HLS tools focussed on the synthesis of behavioural descriptions in HDLs, instead of regular programming languages: the learning curve for these languages prohibited the adoption by algorithm designers. The (late) 2000's saw the (commercial) introduction of HLS tools that use the programming language C as the input specification language. Such tools include Catapult-C [8] and AutoPilot [77]. This significantly lowered the bar for algorithm designers and normal programmers to use these tools.

```

package types is

type array_of_signed_16 is array (natural range <>)

of signed (15 downto 0);

type array_of_signed_32 is array (natural range <>)

of signed (31 downto 0);

end:

6

entity fir is

generic (NUM TAPS: natural);

std logic;

port (clk

: in

: in

std logic;

rstn

11

signed (15 downto 0);

inp

: in

12

array_of_signed_ 16 (NUM_TAPS-1 downto 0);

coeffs

: in

: out signed (15 downto 0));

outp

14

end;

15

16

architecture rtl of fir is

signal reg, reg next: array of signed 16 (NUM TAPS-1 downto 0);

18

: array_of_signed_ 32 (NUM_TAPS-1 downto 0);

19

begin

2.0

-- register

21

process (clk, rstn)

22

begin

23

if rstn = '0' then

reg \ll (others \Rightarrow (to\_signed(0,16)));

25

elsif rising_edge (clk) then

26

reg <= reg\_next;

27

end if:

28

end process;

29

30

-- combinational logic

31

reg_next <= inp & reg(NUM_TAPS-1 downto 1);</pre>

32

33

mul_add_coeffs : for i in (NUM_TAPS-1) downto 0 generate

34

begin

35

mul\_initial: if i = (NUM\_TAPS-1) generate

36

temp(i) \le reg(i) * coeffs(i);

37

end generate;

38

39

mul\_add\_rest: if i \neq (NUM\_TAPS-1) generate

40

temp(i) \le temp(i+1) + (reg(i) * coeffs(i));

41

end generate;

42

end generate;

43

outp \le temp(0)(32 \text{ downto } 16);

45

end;

46

```

Advances in compiler technology, and a focus on the digital signal processing (*DSP*) parts (instead of the control parts) within circuit designs, has resulted in a much higher quality of the hardware that is generated by contemporary HLS tools [12, 41]. That does not mean that arbitrary C programs can be converted to highly performing circuits: they almost always have to be altered so that the HLS tools can infer more parallelism. Also, although HLS tools are very good at extracting instructionand loop-level parallelism from C programs, extracting task-level parallelism still requires manual annotation [12].

The problems that HLS tools face stems from the sequential, imperative, nature of the languages that are used for specification, and the parallel, immutable, nature of digital circuits. Even the most commonly used HDLs are based on languages that were created for sequential CPUs: VHDL is based on Ada, and Verilog on C. It thus makes sense to explore languages that are not created with a sequential platform in mind, and are hopefully better aligned with the parallel nature of digital circuits.

#### 1.2 FUNCTIONAL HARDWARE DESCRIPTION LANGUAGES

The third, lesser travelled and lesser known, road to raising the abstraction level of circuit design is to use a programming paradigm that falls outside of the scope of *imperative* languages. The most studied, non-imperative, paradigm in the context of circuit design is *functional* programming. The tenets of functional programming are simply *function abstraction*, the creation of functions, and *function application*. Two other features often associated with functional languages are *purity* and *immutability*, where the two are actually closely related.

Purity is used to indicate that a function always returns the same result for an associated input; that is, the result is not influenced by side-effects, nor does a function produce any side-effects. As mutation is a side-effect, variables in pure functional languages are immutable. A variable in a functional language is thus akin to a variable in mathematics: a constant, yet unknown, value.

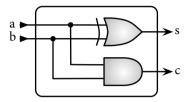

The *combinational logic* in a digital circuit is a logic function, in the mathematical sense, from its inputs to its output. The *pure* functions as those found in functional languages embody this function concept of mathematics. *Pure* functions are thus a perfect model for the *combinational logic* in digital circuits. The code in listing 1.3, describing a half adder circuit, serves as a small example to demonstrate the correspondence between functional descriptions and digital circuits.

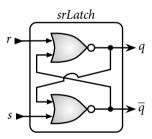

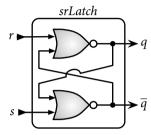

Just like the mathematical function concept they embody, functions in functional languages are timeless: there is no notion of time that influences their behaviour. Circuits on the other hand have *propagation delays*: it takes time for a level change to propagate through a circuit. The retention behaviour of memory elements in *sequential logic* crucially depends on these propagation delays. So, although listing 1.4 is a good structural description of the combinational logic of an SR latch, the semantics of the description does not say anything about the propagation delays and hence the retention behaviour of the SR latch.

```

halfAdder\ a\ b=(s,c)

```

- where

- $s = xor \ a \ b$

- $c = and \ a \ b$

#### Circuit

Listing 1.3 - Half adder

#### Structural description

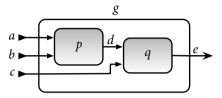

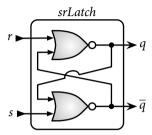

- srLatch r s = (q, nq)

- 2 where

- q = nor r nq

- nq = nor q s

#### Circuit

LISTING 1.4 - SR Latch

Perhaps initially it seems that *pure* functions are thus a rather poor fit to *model* sequential logic. In the next subsection we will, however, show how sequential logic can still be captured intuitively in a functional language.

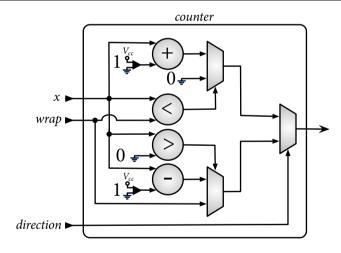

#### 1.2.1 SEQUENTIAL LOGIC

Sequential logic in digital circuits can be divided into *synchronous* and *asynchronous* logic. In synchronous logic, all memory elements update their state in response to a clock signal. In asynchronous logic, memory elements can update their state at any time in response to a changing input signal. Although we can describe asynchronous sequential circuits in a functional language [2], in this thesis we

```

1 dflipflop :: a -- Initial (or reset) value

2 \rightarrow [a] -- Input signal

3 \rightarrow [a] -- Output: input signal where all samples are delayed

4 -- by 1 cycle

5 dflipflop i s = i: s -- place inital value in front of the incoming samples

```

#### Derived circuit

LISTING 1.5 - D flip-flop

restrict ourselves to synchronous sequential logic.

The clock signal in synchronous logic is an oscillating signal that is distributed to all the memory elements such that they all observe its level change simultaneously. A crucial aspect of synchronous logic is that the interval of the clock signal must be long enough so that the input signals of the memory elements can reach a stable value. The time it takes for a signal to become stable is determined by the largest propagation delay between any two memory elements with no other memory element in between. The (combinational) logic between memory elements must hence be completely acyclic. Synchronous design allows a designer to abstract from propagation delays, and reason about state changes as if they happen instantaneously and synchronised.

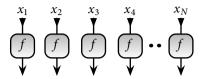

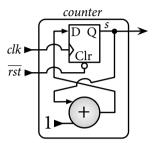

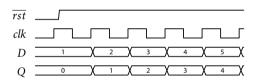

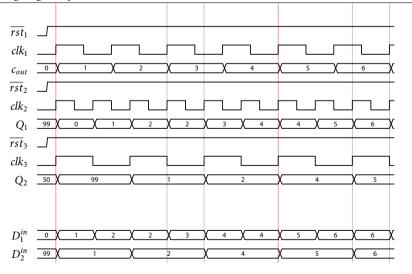

Now that we can abstract away from propagation delays in synchronous sequential logic, it becomes more straightforward to model this sequential logic in a pure functional language. Where combinational logic can be modelled by functions that work on elementary values (booleans, integers, etc.), synchronous sequential logic can be modelled by functions that work on *streams* of elementary values. The elements in the stream correspond to the stable values for the consecutive clock ticks.

Memory elements can now be modelled as functions that add elements to the head a stream (see listing 1.5): given an stream of values s, adding a value i to the head results in a new stream, s, in which every value in s is *delayed* by one clock cycle. Values calculated at time t are now available at time t+1. Directly working with streams can be confusing, and can lead to anti-causal descriptions (by dropping values from the stream); it is thus safer to only expose a set of primitives for stream manipulation. This aspect will be elaborated further in chapter 3.

Until now we have only discussed how to *model* sequential logic in a functional language. That doesn't mean, however, that all functional language based approaches

```

\begin{array}{ll}

map f [] &= [] \\

map f (x:xs) &= f x : map f xs

\end{array}

```

#### Structural view

Listing 1.6 – *map*: parallel composition of a unary function

to hardware design need explicit descriptions of sequential logic. In chapter 2 we will see approaches where functions are a purely behavioural description, and the synthesis tool will infer, or generate, sequential logic where appropriate.

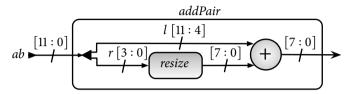

#### 1.2.2 HIGHER LEVEL ABSTRACTIONS

While the semantic match between functional languages and digital circuits is a great technical feature, it does not directly offer the higher-level abstractions needed by hardware engineers to be productive. Where other high-level HDLs get their new design abstractions from the object-oriented programming paradigm, such as classes and interfaces in SystemVerilog, *functional* HDLs gain their high level of abstraction from their straightforward manipulation of *functions*. These so-called higher-order functional languages have functions that can receive *functions* as their arguments, or return *functions* as a result.

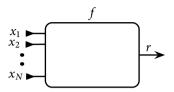

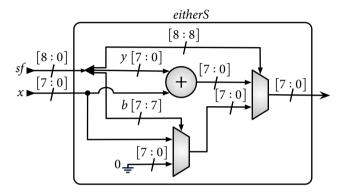

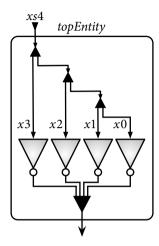

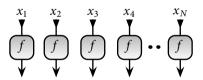

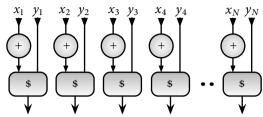

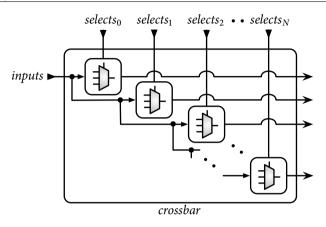

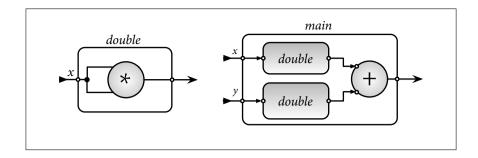

Higher-order functions allow many forms of design abstraction. One example is, of course, parametrising parts of the functionality of a circuit description. More generally, it is possible to capture certain design and recursion patterns as a function; where the latter are called *recursors*. One such *recursor* is the *map* function, shown in listing 1.6, which takes two arguments, a function f and a list f and applies the f to all elements in f and we take a structural view of the f the function (bottom part of listing 1.6), we see that application of f translates to a parallel composition of the circuit f. Aside from parallel composition, higher-order functions can capture many more connection and composition patterns commonly found in digital circuits. Further benefits of higher-order functions and *recursors* will be discussed in greater detail in chapter 3.

Another abstraction found in functional languages is polymorphism, where a function is not tied to a fixed type for every argument, but can work on arguments of any type. Combined with strong static typing and extensive and principled type *inference*, designers can write functions that are:

- » Reusable and parametric: due to polymorphism.

- » Correct: due to strong, static, typing.

- » Concise: due to the absence of type annotations, as types are inferred.

#### 1.2.3 Challenges in synthesising functional HDLs to circuits

We have seen that the semantics of pure functional languages match the semantics of combinational logic when we have functions which process elementary objects, and of sequential logic when we have functions which process streams. Given that there is such a semantic match, synthesis from descriptions made in a functional language to a low-level format, such as a netlist, should thus be straightforward. While this is true for simple functions, synthesis of functions that use higher-level abstraction mechanisms is more difficult. We highlight the synthesis difficulties using the *map* function of listing 1.6 as an example:

- » The *map* function is polymorphic, so we cannot trivially determine how many wires are needed to connect all the components.

- » The *map* function is higher-order, its first argument is a function. We cannot encode functions as bits that flow through wires.

- » The map function is recursive, which is problematic when you view function definitions as structural descriptions of a component. Under such an approach, recursive function applications will be synthesized to self-instantiation of a component. This in turn leads to, unrealisable, infinite structures.

The exact synthesis of functional languages as proposed in this thesis, and further elaboration of the challenges and their solutions, will be described in chapter 4.

Aside from the theoretical challenges of synthesising higher-order and recursive descriptions, there is also the practical burden of implementing the actual simulation and synthesis tools. Especially in the academic setting this has resulted in incomplete toolsets. One popular approach to alleviate the implementation burden is to create an *embedded* domain specific language (*DSL*) for circuit design, which is the approach taken by, for example, the Lava HDL [7]. An embedded DSL is, as the name suggests, not a stand-alone language, but actually a library defined within a general purpose language. An embedded language has the syntax of the host language, where the data types and functions of the DSL library act as a new set of keywords.

Synthesis for these embedded languages works in a non-standard way, where the standard way would be performing a static analysis of the source code. The library functions and data types in an embedded language are actually small, composable, circuit generators. Simply executing the top-level function of the design within the host language will generate the complete circuit. One technical difficulty is that these circuit generators will, in the presence of feedback loops, generate infinite trees, which have to be folded back into a graph structure [24]. One deficit of the embedded language approach is that not all of the (desirable) features of the

host-language can be used for circuit description. Most importantly, the choice-constructs (such as case-statements) of the host language cannot be used to describe choice-constructs in the eventual circuit; we will elaborate why in chapter 2. A designer will have to use one of the choice-functions offered by the embedded DSL library; which are often inferior in terms of expressibility compared to those offered by the host language.

#### 1.3 RESEARCH QUESTIONS

The main goal of this thesis is to *further improve the productivity of circuit designers*. As shown in the previous sections, there are multiple avenues we could explore in order to achieve higher productivity. In this thesis we chose to further explore the domain of functional hardware description languages, due to the semantic match between functional languages and digital circuits, and the high-level abstraction mechanisms available in functional languages. Being more productive is, however, not just achieved by being able to abstract functionality, we also need:

- » To be able to express common idioms in circuit design straightforwardly.

- » Decrease the amount of time spent on the verification of circuit designs.

- » Reason confidently about non-functional properties, such as chip area and gate propagation delays.

This thesis therefore seeks answers to the following questions:

- » How can functional languages be used to express both combinational *and* sequential circuits idiomatically?

- » How can we support correct-by-construction design methodologies using a functional language?

- » How can we use the high-level abstractions without losing performance, and have a straightforward cost model?

#### 1.4 APPROACH AND CONTRIBUTIONS OF THE THESIS

In a previous section we described the use of *embedding* in order to create a new HDL, but then also highlighted that the embedded approach has its own problems. Instead of either embedding a HDL in a functional language, or creating a completely new language from scratch, this thesis explores the idea of using an existing functional language *directly* for the purpose of circuit description.

This thesis makes the choice of using the functional language *Haskell* for circuit design. We choose Haskell because of the many abstractions offered by its expressive type-system, polymorphism, higher-order functions, and pattern-matching constructs. Haskell's extensive type-derivation and near lack of syntax and keywords additionally leads to readable and concise circuit descriptions. Although there

are other functional languages which have very similar properties, we specifically choose Haskell because:

- » It is a *pure* functional language, meaning that it has *pure* functions, which, as mentioned earlier, map very well to combinational logic.

- » It has a non-strict semantics, meaning that arguments to a function are only evaluated when their value is needed; the advantages of which are described in chapter 3.

Also, instead of creating a complete toolset from scratch, we adapt an existing Haskell compiler. We start with the existing Glasgow Haskell compiler (*GHC*) [64] and its associated libraries and tools. We extend the set of libraries with a library that has circuit-specific data types and functions, such as: arbitrary-width integers, registers, etc. Since our circuits are just Haskell programs, simulation is done in GHC by either:

- » Applying a circuit description to its inputs within the GHC Haskell interpreter, or, if extra simulation speed is desired,

- » Compiling the circuit description, together with its inputs, into an (optimized) executable, and execute the compiled program.

Aside from having designed a library for circuit design, we have also created a synthesis tool that converts the Haskell descriptions to low-level, synthesisable, VHDL. Also for this synthesis tool we can reuse large parts of GHC, which exposes its internals as a library. Our efforts mainly focussed on the synthesis of GHCs intermediate language, which is much smaller than Haskell. We used the GHC library functions for parsing and type checking.

One advantage of embedded DSLs not explicitly discussed earlier is that the evaluation mechanism of the host-language eliminates all high-level abstractions, such as higher-order functions. This means that the embedded DSL implementer does not have to deal with the synthesis of these abstractions. By choosing a standard synthesis approach based on static analysis for this thesis, *we* do, however, have to deal with the synthesis of these abstraction mechanisms explicitly.

#### Contributions

For the synthesis of these higher-level abstraction mechanisms, we chose an approach which is classic in the compilation of functional languages: compilation-by-transformation. In compilation-by-transformation, source-to-source transformations are applied exhaustively until the description has such a shape that a mapping to the target architecture is straightforward. Existing approaches are designed with instruction-set machines in mind: directly mapping their output to digital circuits would lead to highly inefficient circuits. We will elaborate on these inefficiencies in chapter 4. This thesis explores a term rewrite system (*TRS*), a specific form of

compilation-by-transformation, that removes abstraction mechanisms from a description that have no direct mapping to a digital circuit, but without introducing any inefficiencies.

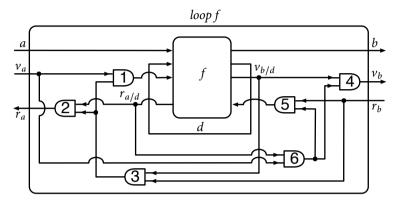

This thesis is a continuation of the work done in [4] and [38], which resulted in the original prototype for the synthesis tool and circuit library: "CAES language for synchronous hardware  $(C\lambda aSH)$ ". We want to note that, from now on, we will refer to the triple: Haskell, our library for circuit design, and our synthesis tool, as the  $C\lambda aSH$  language. This thesis improves upon [4] and [38] by providing a better approach for the *composition* of sequential circuit specifications, which we will discuss in chapter 3. Additionally, the rewrite system described in chapter 4 can correctly synthesise a larger class of specifications than the system described in [38], and also comes with a correctness proof.

#### 1.5 STRUCTURE OF THE THESIS

The next chapter starts with an overview of a select number of hardware description languages, focusing mostly on industrially used languages such as VHDL and Verilog, and on *functional* HDLs. The chapter will highlight the merits and disadvantages of the individual languages, the details of their synthesis (and problems therein), and compare them to the  $C\lambda$ aSH language.

The subsequent chapter, chapter 3, describes the C $\lambda$ aSH language in greater detail. It highlights how the abstraction mechanisms in functional languages are highly beneficial in the creation of high-level, parametric, circuit designs. One important aspect discussed in length is how C $\lambda$ aSH deals with the concept of *state*. Additionally, we make our case for basing C $\lambda$ aSH on a *non-strict* language, as opposed to a *strict* language.

In chapter 4 we delve into the aspects of the synthesis from  $C\lambda aSH$  to netlist-level VHDL. We discuss both the general setup of the  $C\lambda aSH$  compiler, and in greater depth the term rewrite system (TRS) that removes abstractions such as higher-order functionality. The chapter highlights the importance of *types* in synthesis, and how they guide the synthesis process. Correctness of the transformations, completeness of the system (that all abstractions with no counterpart in a digital circuit are removed), and termination of the  $C\lambda aSH$  compiler, are important aspects, and are discussed in this chapter.

Usability and effectiveness of the  $C\lambda$ aSH language and compiler are demonstrated in chapter 5 using several mid-size circuit designs. These designs cover both data and control oriented aspects found in digital circuits.

Finally, this thesis concludes with chapter 6, where we discuss and summarise what we have achieved by building the  $C\lambda$ aSH language and compiler. Specifically, we will address the advantages and disadvantages of using a general-purpose functional programming language Haskell as a starting point for a HDL. The chapter ends with recommendations for further research.

# 2

## HARDWARE DESCRIPTION LANGUAGES

ABSTRACT – In order to increase productivity, hardware description languages must have the ability to abstract common idioms and patterns. Over the years, conventional hardware description languages have acquired more methods for abstraction, but these new aspects are sometimes non-trivial to use or are limited in scope as to what they are able to abstract. New languages have more powerful abstraction mechanisms, but as a result, their synthesis to RTL has become more complex, and is in certain situations limited. These limitations in synthesis also limits the expressivity of the designer. We compare the abstraction capabilities of existing hardware description languages, and their respective limitations, and elaborate where  $C\lambda aSH$  either makes improvements or makes a different trade-off.

#### 2.1 Introduction

There are many description languages for hardware, both analogue and digital, and their introduction and revision dates span several decades. In the context of this thesis we will, however, focus on languages for synchronous, digital, circuit design; or at least those languages of which their synthesis tools produce a synchronous digital circuit. We narrow the overview of HDLs and their comparison with the  $C\lambda$ aSH language even further to those languages that are currently accepted in industry (such as Verilog), and existing *functional* HDLs. The comparison with the industrially accepted languages is there to warrant the research into new HDLs in general, where the comparison with functional HDLs is there to demonstrate

that  $C\lambda aSH$  captures a new and relevant point in the design space in the field of functional HDLs in particular.

For the languages such as VHDL and Verilog we describe the design abstraction available, and which parts of these languages are synthesisable. As  $C\lambda$ aSH distinguishes itself as a new point in the design space of functional HDLs, we will describe these functional languages in more detail. Also their synthesis is discussed in more detail, as this aspect usually plays an important role (and not an afterthought as it was for VHDL) in the features available in these languages.

#### 2.2 STANDARD HARDWARE DESCRIPTION LANGUAGES

With *standard* languages we mean HDLs that are commonly used in industry, taught in courses on digital design, and have support in tools from multiple vendors. These languages are: VHDL, Verilog, and by extension SystemVerilog.

#### 2.2.1 VHDL

VHDL has several abstractions available that allow for parametric and generative circuit design: *generics* (c.f. listing 2.1) and *configurations* on the parametric side, and *generate statements* (c.f. listing 2.2) on the generative side. This section only gives a short overview of these language features to demonstrate the means of abstraction in VHDL. Completely elaborating these features falls outside the scope of this thesis, and we refer the reader to works such as [3] for further details.

#### Parametrisation

In VHDL, design entities can be parametrised by certain *constant* values using *generics*. As of VHDL-2008 [34], the generics have been extended to: type, function, and package generics. Type generics basically added a form of polymorphism to the VHDL language, where function generics add higher-order functionality. An example of a polymorphic, higher-order, entity is shown in listing 2.1. There are several caveats to these new generics:

- » Support for VHDL-2008, especially for the new generics, is either non-existent or fairly limited in synthesis tools<sup>1</sup>.

- » Functions only support the sequential subset of VHDL, not the concurrent one. There is hence no means to parametrise a component in concurrent logic using generics, a designer must use configurations for this.

- » Explicitly mapping every type generic is tedious and error-prone, especially when compared to type-inference which is prevalent in functional languages.

<sup>&</sup>lt;sup>1</sup>At the time of this writing, the only synthesis tool that we have found to fully support type and function generics is: Synopsys Synplify(Pro/Premier), version I-2013.09-1

```

entity incrementer is

generic (type data_type;

function increment (x: data_type) return data_type);

port (inp : in data_type;

outp : out data_type;

inc : in std_logic);

end;

architecture rtl of incrementer is

begin

outp <= increment(inp) when inc = '1';

end;

```

LISTING 2.1 – Type and Function Generics

Aside from generics, there are also *configurations* as a means for parametrisation. Using configurations, declared component interfaces can be instantiated to different design architectures. This can be performed globally using a configuration *declaration*, or locally, using a configuration *specification* in the declarative part of e.g. a *block* declaration. Where configuration *declarations* can be used to configure any instantiated component in the design hierarchy, configuration *specifications* can only be used to configure components in the same scope as the configuration specification.

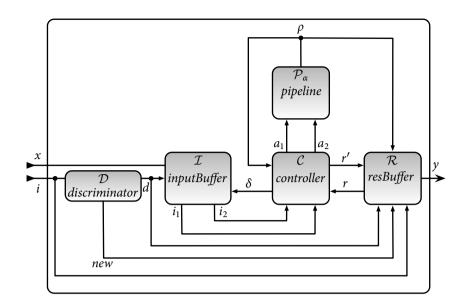

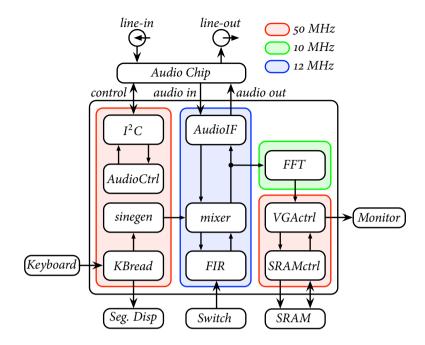

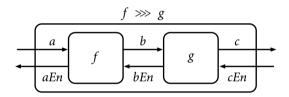

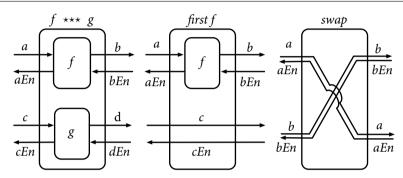

A disadvantage of configurations and component declaration is that this configurability, unlike generics, is not visible at the interface of a design, its entity declaration. You cannot pass a configuration from one component to the other; whereas generics can be passed from one component to the other. This makes configurations highly non-modular, they are *only* useful in the context of a complete design hierarchy.